### (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2005/0017964 A1

Yamazaki et al.

Jan. 27, 2005 (43) Pub. Date:

### (54) **DISPLAY DEVICE**

(75) Inventors: Shunpei Yamazaki, Tokyo (JP); Jun Koyama, Kanagawa (JP); Mitsuaki Osame, Kanagawa (JP); Mai Osada,

Kanagawa (JP)

Correspondence Address: FISH & RICHARDSON P.C. **1425 K STREET, N.W.** 11TH FLOOR WASHINGTON, DC 20005-3500 (US)

(73) Assignee: Semiconductor Energy Laboratory Co., Ltd., a Japan corporation

(21) Appl. No.: 10/920,326

(22) Filed: Aug. 18, 2004

### Related U.S. Application Data

(63) Continuation of application No. 09/833,673, filed on Apr. 13, 2001, now abandoned.

#### (30)Foreign Application Priority Data

| Apr. 18, 2000 | (JP) | ١ | 2000-117045 |

|---------------|------|---|-------------|

|               |      | · |             |

### **Publication Classification**

| (51) | Int. Cl. <sup>7</sup> |  |

|------|-----------------------|--|

| (52) | U.S. Cl.              |  |

### **ABSTRACT** (57)

The present invention is intended to suppress power consumption of an EL display. In accordance with the brightness of an image to be displayed in a pixel portion, the contrast of the image is determined whether to be inverted or not, and the number of bits of the digital video signal to be input into the pixel portion is reduced, and the magnitude of a current to flow through the EL element is allowed to be maintained at a constant level even when a temperature of an EL layer changes by providing the EL display with another EL element to be used for monitoring a temperature.

Fig. 1

Fig. 2

Fig. 3

Fig. 4

Fig. 5

# to pixel electrode in pixel portion

Fig. 6

Fig. 7

Fig. 9

Fig. 10

Fig. 11

Fig. 12

Fig. 1:

Fig. 14 801 831b 831a 836 837a. 837b 832a. 832b 838a 833a 838b 833b -839 834a 841 .834b

Fig. 15A

Fig. 15B

102-4

863

862

to source signal line

Fig. 16

-ig. 17

Fig. 18A

Fig. 18B

Fig. 19

ig. 26-

Fig. 21

# to pixel electrode in pixel portion

Fig. 22

Fig. 27B

Fig. 29A

Fig. 29B

### **DISPLAY DEVICE**

### BACKGROUND OF THE INVENTION

[0001] 1. Field of the Invention

[0002] The present invention relates to a display panel in which a light emitting element formed on a substrate is sealed between the substrate and a cover member. In addition, the present invention also relates to a display module in which an IC chip is mounted on the above-mentioned display panel. It should be noted that in the present specification, the display panel and the display module are collectively referred to as the light emitting device. The present invention further relates to an electronic apparatus that employs the above-mentioned light emitting device.

[0003] 2. Description of the Related Art

[0004] Recently, techniques for forming a TFT on a substrate has been greatly advanced, and much developments have been made to apply those techniques to an active-matrix type display device. In particular, a TFT employing a poly-crystalline silicon film can operate at a higher speed since a field effect mobility (simply referred to as the mobility) thereof is larger than that of a TFT employing the conventional amorphous silicon film. Thus, it becomes possible to control pixels by means of a driver circuit formed on the same substrate as the pixels. Such the pixels was conventionally controlled by means of a driver circuit provided at the outside of the substrate.

[0005] The active-matrix type display device as mentioned above can exhibit various advantages such as a reduced fabricating cost, miniaturization of the display device, an increased fabricating yield, a reduced throughput or the like, by providing various circuits and elements on the identical substrate.

[0006] Furthermore, developments of an active-matrix type light emitting device having light emitting elements as a self-emission type element have been actively conducted. Such a light emitting device is also referred to as an Organic EL Display (OELD) or an Organic Light Emitting Diode (OLED).

[0007] Unlike a liquid crystal display, the light emitting device is of the self-emission type. The light emitting element has a structure in which a layer containing an organic compound (hereinafter referred to as the organic compound layer) that allows luminescence to be generated by applying an electrical field thereto is interposed between a pair of electrodes (an anode and a cathode). The organic compound layer usually has a layered structure. Typical examples therefor include a layered structure of "a hole transportation layer/a light emitting layer/an electron transportation layer" proposed by Tang et al. of Eastman Kodak Co. This structure has a high luminous efficiency, and most of light emitting devices about which research and development activities are currently being progressed employ this structure.

[0008] Although a luminescence in an organic compound includes a singlet excitation (fluorescence) and a triplet excitation (phosphorescence), the light emitting device of the present invention can use one or both of the above luminescence.

[0009] Alternatively, a layered structure in which a hole injection layer/a hole transportation layer/a light emitting layer/an electron transportation layer, or a hole injection layer/a hole transportation layer/a light emitting layer/an electron transportation layer/an electron injection layer are formed on an anode in these orders may be used. Furthermore, fluorescent dyes or the like may be doped into the light emitting layer.

[0010] In the present specification, all of the layers to be disposed between the cathode and the anode are collectively referred to as the organic compound layer. Accordingly, all of the above-mentioned layers such as the hole injection layer, the hole transportation layer, the light emitting layer, the electron transportation layer, the electron injection layer or the like are included in the organic compound layer.

[0011] A predetermined voltage is applied to the organic compound layer made of the above-mentioned structure via the pair of electrodes, and thus recombination of carriers occurs in the light emitting layer, thereby resulting in light emission. In the present specification, when the light emitting element emits light, the light emitting element is expressed as being driven. In addition, in the present specification, the light emitting element composed of an anode, an organic compound layer, and a cathode is referred to as the light emitting element.

[0012] Since the light emitting device is not required to employ a back light, a thickness and a weight of the display itself can be suppressed, as compared to a liquid crystal display. For that reason, the light emitting device has come to be used as a display section of a portable information terminal (a mobile computer, a portable telephone, a portable game apparatus, an electronic book or the like), instead of the liquid crystal display.

[0013] In order to suppress power consumption of the portable information terminal, it has been desired to suppress power consumption of the light emitting device to be employed as the display section.

[0014] Moreover, digitalization of a receiver or a VTR to be used in home as well as various equipment to be used in a TV or radio broadcast station has now proceeded. As the next step following digitalization of a broadcast system is digitalization of broadcast electric waves, i.e., realization of digital broadcasting. Vigorous research and development activities have been performed toward such a goal.

[0015] One scheme to be used for realizing a digital driving of the light emitting device is a temporal gradation display. More specifically, the temporal gradation display refers to a driving method in which the gradation display is performed by controlling a time period during which the light emitting element is to emit light in one frame period.

[0016] In the case where the light emitting device is digitally driven to perform the temporal gradation display, the required number of rewriting a digital video signal containing image information to be input to pixels is increased, as the number of gradation of an image to be displayed is increased. Consequently, power consumption of a group of driver circuits to be used for inputting the digital video signal into the pixels is increased, thereby resulting in increased power consumption of the light emitting device.

[0017] In addition, since the light emitting element is of the self-emission type, a time period during which the light

emitting element is to emit light in one frame period varies depending on an image to be displayed. Accordingly, power consumption of the light emitting device in turn varies depending on an image to be displayed.

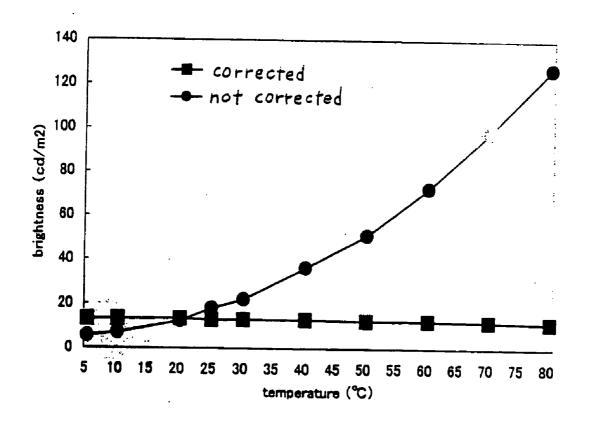

[0018] Furthermore, the magnitude of a current to flow through the light emitting element varies also depending on temperature. Even with a voltage of the same magnitude being applied across the electrodes of the light emitting element, the magnitude of a current to flow through the light emitting element varies due to temperature characteristics of the light emitting element. For example, as the temperature of the organic compound layer increases, a larger current tends to flow. Accordingly, as an environmental temperature under which the light emitting element is to be used increases, power consumption of the light emitting device increases, which in turn increases the brightness of the light emitting element.

[0019] In view of the above-described situations, the present invention is intended to suppress power consumption of a light emitting device and an electronic apparatus employing the light emitting device as its display section.

### SUMMARY OF THE INVENTION

[0020] A first structure according to the present invention is characterized in which in the case where a monochrome display is performed in a light emitting device, the contrast of an image is determined whether to be inverted or not in accordance with what kind of an image to be displayed by pixels in a pixel portion.

[0021] In accordance with the above-mentioned structure, the magnitude of a current to flow through the light emitting element can be suppressed to some degree, thereby resulting in a reduced power consumption of the light emitting device.

[0022] Furthermore, a second structure in accordance with the present invention is characterized in that in a light emitting device that performs a digitally-driven time-divisional gradation display, a digital video signal input to a source signal line driver circuit included in the light emitting device is input into a pixel portion after its number of bits is reduced. More specifically, a bit of the digital video signal is sequentially cut off from the least significant bit to reduce the number of bits of the digital video signal to be input into the pixel portion.

[0023] In accordance with the above-mentioned structure, since the number of bits of the digital video signal to be input into the pixels is reduced, the required number of writing the digital video signal by the source signal line driver circuit and a gate signal line driver circuit can be reduced. Thus, power consumption of the source signal line driver circuit and the gate signal line driver circuit can be reduced, thereby resulting in a reduced power consumption of the light emitting device.

[0024] Moreover, in accordance with a third structure of the present invention, a light emitting device is provided with a light emitting element for monitoring a temperature. One of electrodes of the temperature-monitoring light emitting element is connected to a constant current source. Thus, by means of temperature characteristics of the temperature-monitoring light emitting element, the magnitude of a current to flow through a light emitting element of a pixel is maintained at a constant level.

[0025] In accordance with the above-described structure, the magnitude of a current to flow through the light emitting element of a pixel is maintained at a constant level, even when a temperature of the organic compound layer changes. Thus, power consumption of the light emitting device can be prevented from increasing even when an environmental temperature of the light emitting device increases, which in turn can maintain the brightness at a constant level.

[0026] In accordance with the first, second, and third structures of the present invention as described in the above, it is possible to suppress the power consumption of a light emitting device and an electronic apparatus which employs the light emitting device. It should be noted that only either one of the first through third structures is required to be included in the present invention, although two or all of the first through third structures may be included.

[0027] Structures in accordance with the present invention will be further described below.

[0028] The present invention provides a display device having a plurality of pixels, wherein a polarity of a digital video signal to be input into the plurality of pixels is inverted, thereby resulting in brightness of the plurality of pixels being changed.

[0029] The present invention provides a display device having a pixel portion including a plurality of pixels, and a source signal line driver circuit, wherein the source signal line driver circuit includes a switching circuit for switching a polarity of an output, and a polarity of a digital video signal input to the switching circuit is inverted by means of a shift signal to be input into the switching circuit and the resultant signal is then input into the plurality of pixels.

[0030] The present invention provides a display device having a pixel portion including a plurality of pixels, and a source signal line driver circuit, wherein each of the plurality of pixels has a light emitting element, and the source signal line driver circuit includes a shift register, one or more latches and a switching circuit, and a polarity of a digital video signal input from the one or more latches into the switching circuit is inverted by means of a shift signal to be input into the switching circuit and the resultant signal is then input into the plurality of pixels.

[0031] The present invention provides a display device having a pixel portion including a plurality of pixels, and a source signal line driver circuit, wherein each of the plurality of pixels has a light emitting element, and the source signal line driver circuit includes a shift register, one or more latches and a switching circuit, and a polarity of a digital video signal input from the one or more latches into the switching circuit is inverted by means of a shift signal to be input into the switching circuit and the resultant signal is then input into the plurality of pixels, and an average of a time period during which all of the light emitting elements emit light in one frame period is equal to or less than a half of the light emitting elements emit light emitting elements emit light in one frame period.

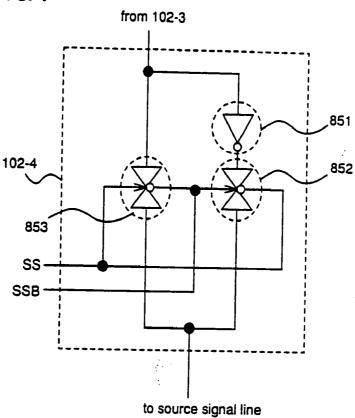

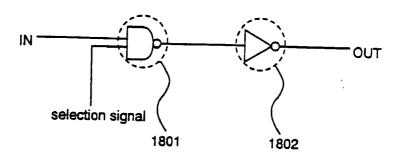

[0032] The above structures may be characterized in which the switching circuit includes an inverter, a first analog switch, and a second analog switch, wherein the digital video signal input into the switching circuit is input into an input terminal of the first analog switch via the inverter, the digital video signal output from the one or more

latches is input into an input terminal of the second analog switch, the shift signal is input from a first control input terminal of the first analog switch and a second control input terminal of the second analog switch, a signal obtained by inverting the polarity of the shift signal is input from a second control input terminal of the first analog switch and a second control input terminal of the first analog switch, and signals output from output terminals of the first analog switch and the second analog switch are output from the switching circuit.

[0033] The above structures may be characterized in which the switching circuit includes an inverter, a first NAND, a second NAND, and a NOR, wherein the first NAND is supplied with the digital video signal via the inverter and the shift signal, the second NAND is supplied with the digital video signal and a signal obtained by inverting a polarity of the shift signal, a signal output from the first NAND and a signal output from the second NAND are input into the NOR, and a signal output from the NOR is output from the switching circuit.

[0034] The present invention provides a display device having a plurality of pixels and a source signal line driver circuit, wherein among a digital video signal to be input into the source signal line driver circuit, only more significant bits are input into the plurality of pixels.

[0035] The present invention provides a display device having a pixel portion including a plurality of pixels, and a source signal-line driver circuit, wherein the source signal line driver circuit includes a shift register, a first latch, a second latch, and a clock signal control circuit, a clock signal is input into the shift register via the clock signal control circuit to thereby output a timing signal from the shift register, a digital video signal is input into and held at the first latch by the timing signal, the digital video signal held at the first latch is input into and held at the second latch by a latch signal, the digital video signal input into and held at the second latch is input into the plurality of pixels, and the clock signal control circuit reduces the number of bits of the digital video signal to be input into and held at the first latch by supplying a constant fixed electrical potential instead of the clock signal to the shift register a constant period of time.

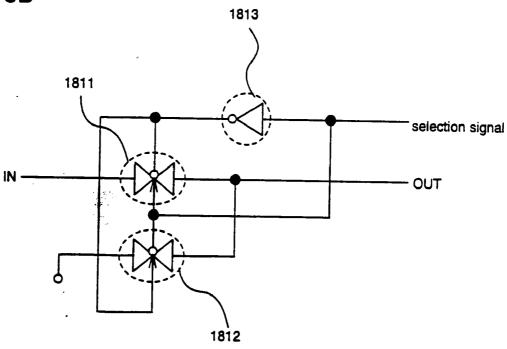

[0036] The above structure may be characterized in which the clock signal control circuit includes a NAND and an inverter, wherein a clock signal and a selection signal are input into the NAND, and a signal output from the NAND is output from the clock signal control circuit via the inverter.

[0037] The above structure may be characterized in which the clock signal control circuit includes a first analog switch, a second analog switch, and an inverter, wherein a selection signal is input via the inverter into a second control input terminal of the first analog switch and a first control input terminal of the second analog switch, the selection signal is input into a first control input terminal of the first analog switch and a second control input terminal of the second analog switch, a clock signal is input into an input terminal of the first analog switch, a fixed electrical potential is supplied to an input terminal of the second analog switch, and signals output from output terminals of the first analog switch and the second analog switch are output from the clock signal control circuit.

[0038] The present invention provides a display device having a pixel portion including a plurality of pixels, and a source signal line driver circuit, wherein the source signal line driver circuit includes a shift register, a first latch, a second latch, and a timing signal control circuit, a timing signal output from the shift register is input into the first latch via the timing signal control circuit, a digital video signal is input into and held at the first latch by the timing signal input into the first latch, the digital video signal held at the first latch is input into and held at the second latch by a latch signal, the digital video signal input into and held at the second latch is input into the plurality of pixels, and the timing signal control circuit reduces the number of bits of the digital video signal to be input into and held at the first latch by supplying to the first latch a constant fixed electrical potential instead of the timing signal output from the shift register for a constant period of time.

[0039] The above structure may be characterized in which the timing signal control circuit includes a NAND and an inverter, wherein a timing signal and a selection signal are input into the NAND, and a signal output from the NAND is output from the timing signal control circuit via the inverter.

[0040] The above structure may be characterized in which the timing signal control circuit includes a first analog switch, a second analog switch, and an inverter, wherein a selection signal is input via the inverter into a second control input terminal of the first analog switch and a first control input terminal of the second analog switch, the selection signal is input into a first control input terminal of the first analog switch and a second control input terminal of the second analog switch, the timing signal is input into an input terminal of the first analog switch, a fixed electrical potential is supplied to an input terminal of the second analog switch, and signals output from output terminals of the first analog switch and the second analog switch are output from the timing signal control circuit.

[0041] The present invention provides a display device having a pixel portion including a plurality of pixels and a source signal line driver circuit, wherein the source signal line driver circuit includes a shift register, a first latch, a second latch, and a start pulse signal control circuit, a start pulse signal is input into the shift register via the start pulse signal control circuit to thereby output a timing signal from the shift register, a digital video signal is input into and held at the first latch by the timing signal, the digital video signal held at the first latch is input into and held at the second latch by a latch signal, the digital video signal input into and held at the second latch is input into the plurality of pixels, and the start pulse signal control circuit reduces the number of bits of the digital video signal to be input into and held at the first latch by supplying to the shift register a constant fixed electrical potential instead of the start pulse for a constant period of time.

[0042] The above structure may be characterized in which the start pulse signal control circuit includes a NAND and an inverter, wherein a start pulse signal and a selection signal are input into the NAND, and a signal output from the NAND is output from the start pulse signal control circuit via the inverter.

[0043] The above structure may be characterized in which the start pulse signal control circuit includes a first analog switch, a second analog switch, and an inverter, wherein a selection signal is input via the inverter into a second control input terminal of the first analog switch and a first control input terminal of the second analog switch, the selection signal is input into a first control input terminal of the first analog switch and a second control input terminal of the second analog switch, a start pulse signal is input into an input terminal of the first analog switch, a fixed electrical potential is supplied to an input terminal of the second analog switch, and signals output from output terminals of the first analog switch and the second analog switch are output from the start pulse signal control. circuit.

[0044] The present invention provides a display device including a plurality of pixels having a plurality of light emitting elements, and a monitoring light emitting element, wherein the magnitude of a current to flow through the plurality of light emitting elements is maintained by means of temperature characteristics of the monitoring light emitting element.

[0045] The present invention provides a display device including a pixel portion including a plurality of pixels, a power source line, a buffer amplifier, a monitoring light emitting element, and a constant current source, wherein each of the plurality of pixels includes a thin film transistor and a light emitting element, each of the monitoring light emitting element and the light emitting element includes a first electrode, a second electrode, and an organic compound layer disposed between the first electrode and the second electrode, the first electrode of the monitoring light emitting element is connected to the constant current source, the first electrode of the monitoring light emitting element is also connected to a non-inverted input terminal of the buffer amplifier, and an output terminal of the buffer amplifier is connected to the power source line, and an electrical potential of the power source line is applied to the first electrode of the light emitting element via the thin film transistor.

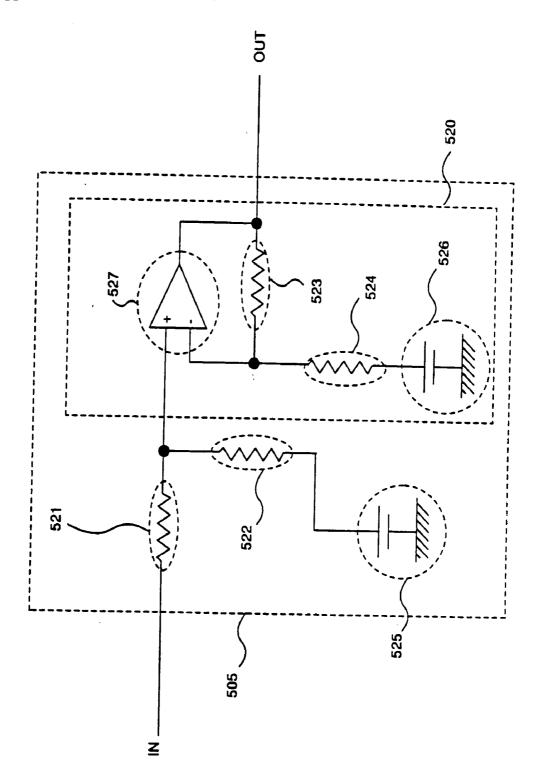

[0046] The present invention provides a display device including a pixel portion having a plurality of pixels, a power source line, a buffer amplifier, a monitoring light emitting element, a constant current source, and an adding circuit, wherein each of the plurality of pixels includes a thin film transistor and a light emitting element, each of the monitoring light emitting element and the light emitting element includes a first electrode, a second electrode, and an organic compound layer disposed between the first electrode and the second electrode, the first electrode of the monitoring light emitting element is connected to the constant current source, the first electrode of the monitoring light emitting element is also connected to a non-inverted input terminal of the buffer amplifier, an output terminal of the buffer amplifier is connected to an input terminal of the adding circuit, an output terminal of the adding circuit is connected to the power source line, a constant potential difference is always maintained between the input terminal and the output terminal of the adding circuit, and an electrical potential of the power source line is applied to the first electrode of the light emitting element via the thin film transistor.

[0047] The present invention may be embodied in the form of a video camera, an image reproduction apparatus, a head mount display, a portable telephone, or a portable information terminal employing the above-mentioned display device.

### BRIEF DESCRIPTION OF THE DRAWINGS

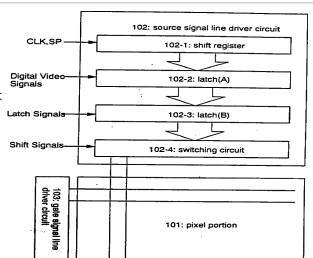

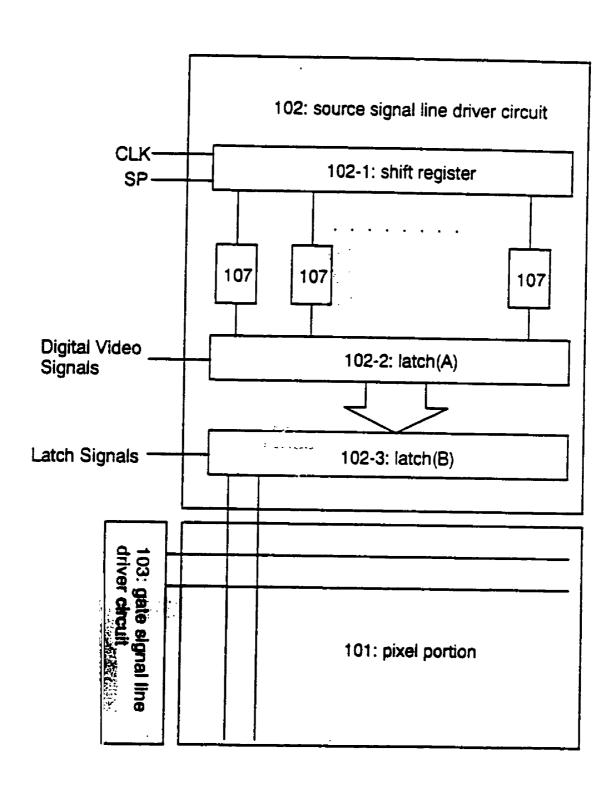

[0048] FIG. 1 is a block diagram of a light emitting device in accordance with the present invention.

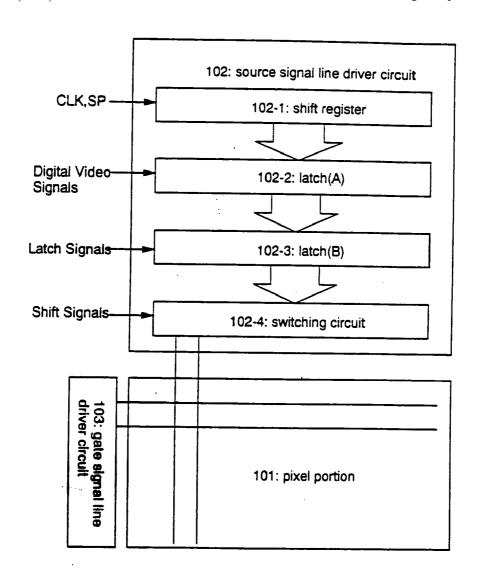

[0049] FIG. 2 is a block diagram of a light emitting device in accordance with the present invention.

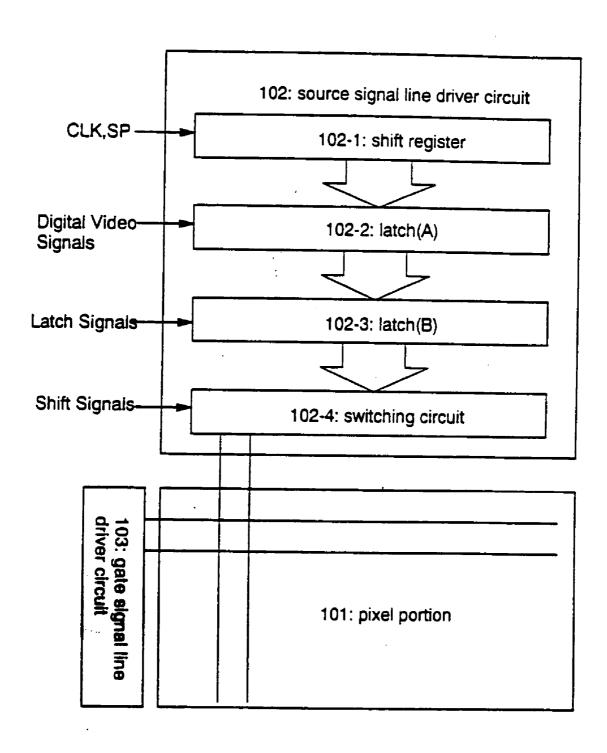

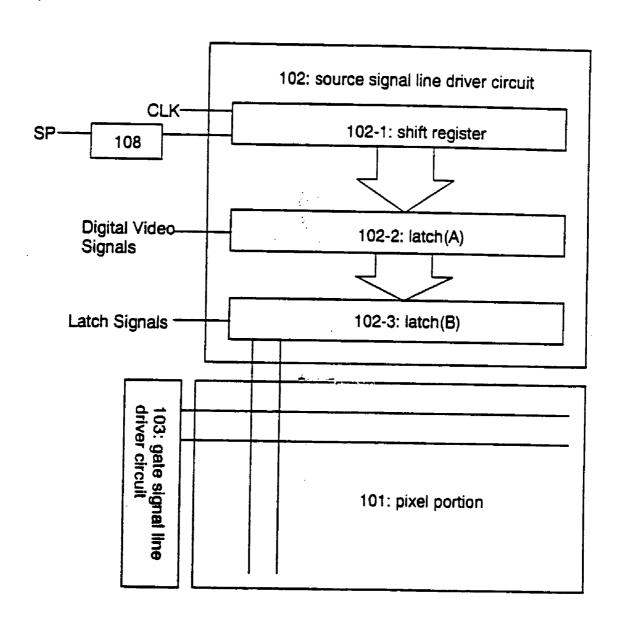

[0050] FIG. 3 is a block diagram of a light emitting device in accordance with the present invention.

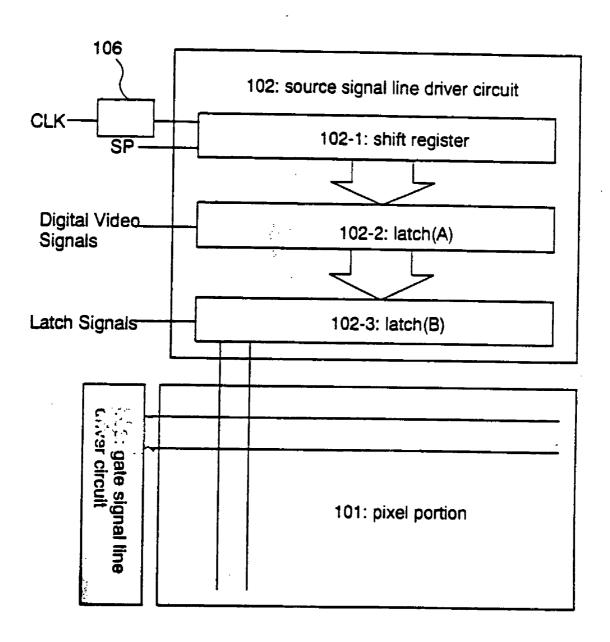

[0051] FIG. 4 is a block diagram of a light emitting device in accordance with the present invention.

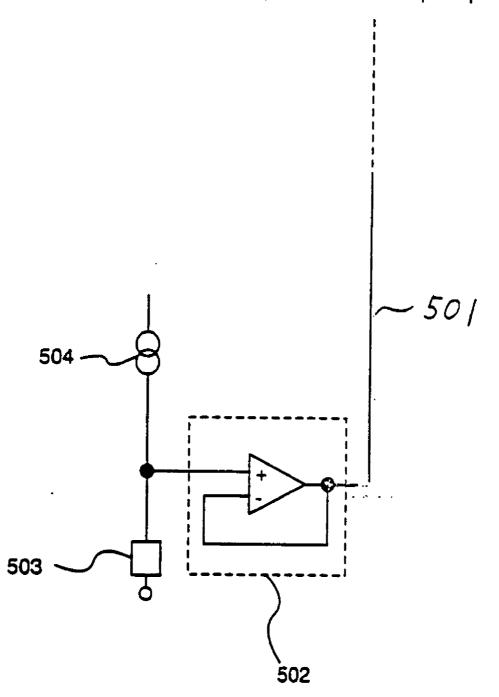

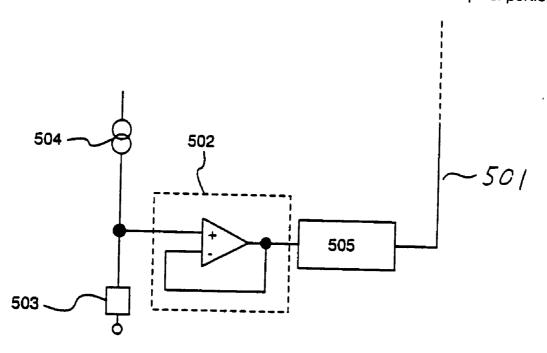

[0052] FIG. 5 is a diagram for illustrating connection of a monitoring light emitting element of a light emitting device in accordance with the present invention.

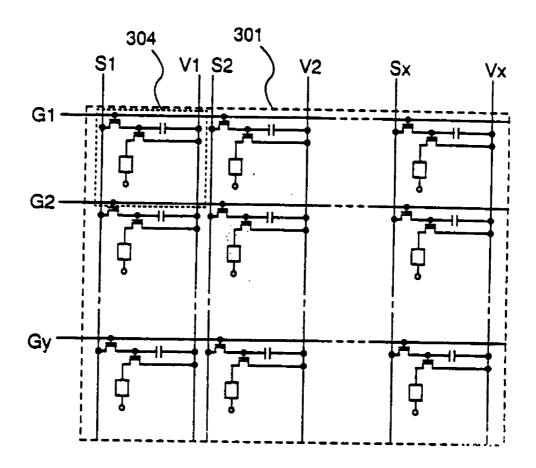

[0053] FIG. 6 is a diagram for illustrating a pixel portion of a light emitting device in accordance with the present invention.

[0054] FIG. 7 is an expanded diagram of a pixel of a light emitting device in accordance with the present invention.

[0055] FIG. 8 is a diagram for illustrating a driving method of a light emitting device in accordance with the present invention.

[0056] FIG. 9 is a block diagram of a light emitting device in accordance with the present invention.

[0057] FIG. 10 is a diagram for illustrating a pixel portion of a light emitting device in accordance with the present invention.

[0058] FIG. 11 is an expanded diagram of a pixel of a light emitting device in accordance with the present invention.

[0059] FIG. 12 is a diagram for illustrating a driving method of a light emitting device in accordance with the present invention.

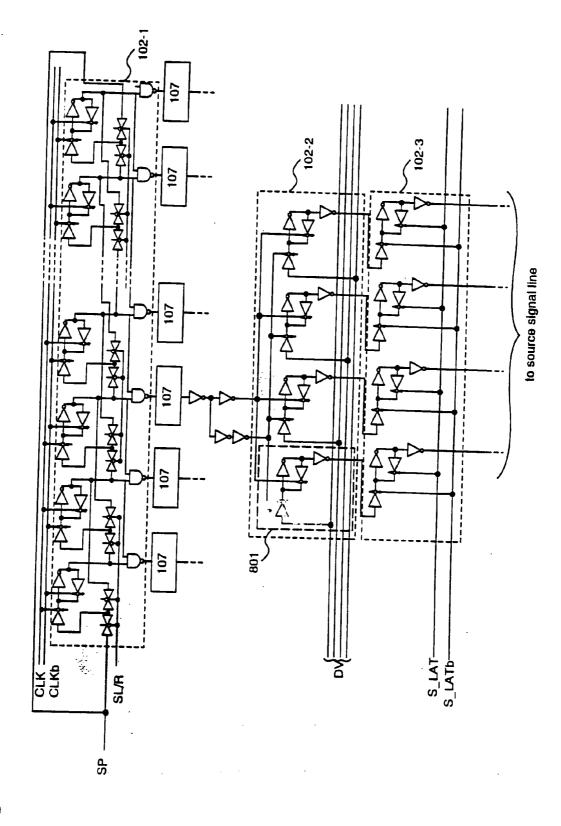

[0060] FIG. 13 is a circuit diagram of a source signal line driver circuit of a light emitting device in accordance with the present invention.

[0061] FIG. 14 is a partial plan view of a latch (A).

[0062] FIGS. 15A and 15B are circuit diagrams of a switching circuit.

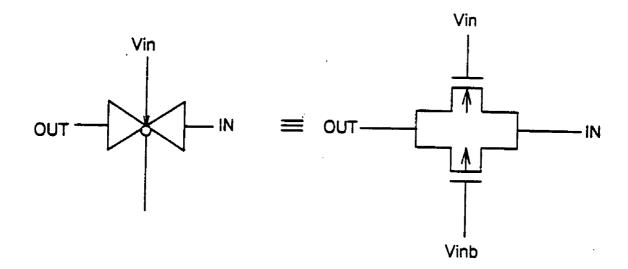

[0063] FIG. 16 is an equivalent circuit diagram of an analog switch.

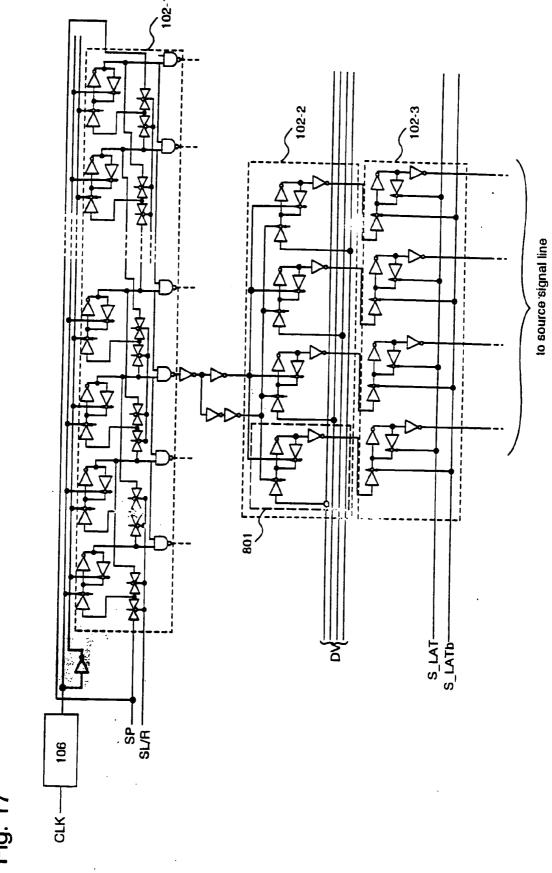

[0064] FIG. 17 is a circuit diagram of a source signal line driver circuit of a light emitting device in accordance with the present invention.

[0065] FIGS. 18A and 18B are circuit diagrams of a clock signal control circuit, a timing signal control circuit, and a start pulse signal control circuit.

[0066] FIG. 19 is a circuit diagram of a source signal line driver circuit of a light emitting device in accordance with the present invention.

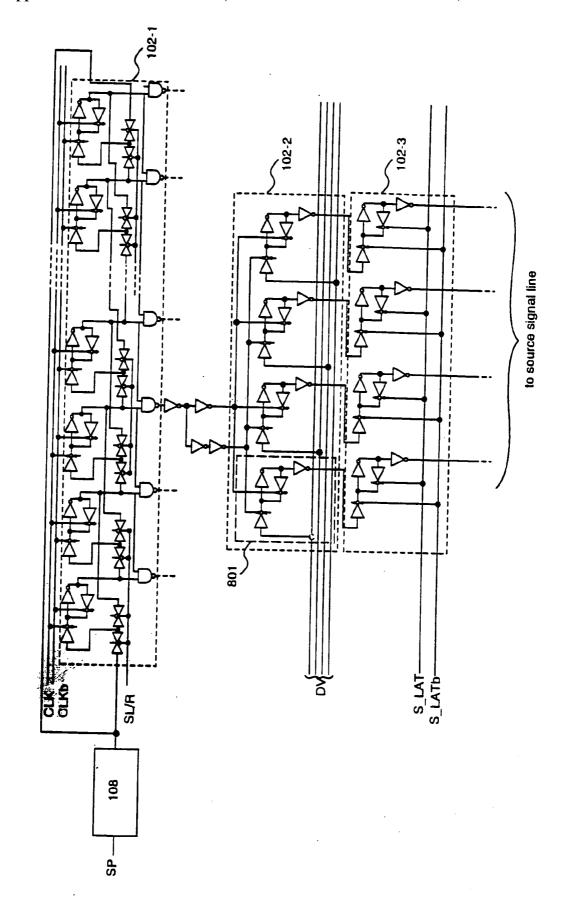

[0067] FIG. 20 is a circuit diagram of a source signal line driver circuit of a light emitting device in accordance with the present invention.

[0068] FIG. 21 is a diagram for illustrating connection of a monitoring light emitting element of a light emitting device in accordance with the present invention.

[0069] FIG. 22 is a circuit diagram of an adding circuit.

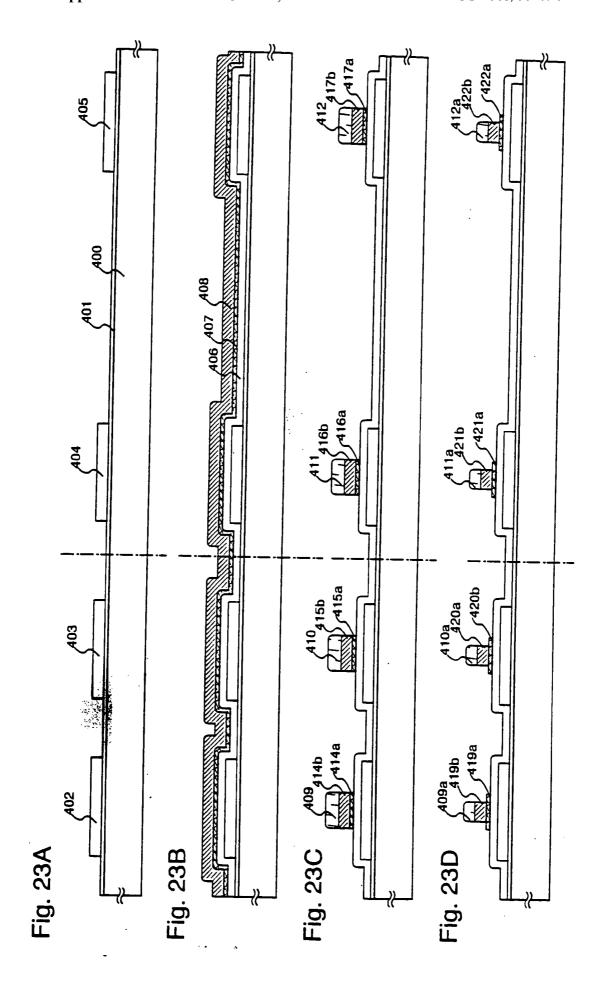

[0070] FIGS. 23A through 23D are cross-sectional views for illustrating various steps of a fabricating method of a light emitting device.

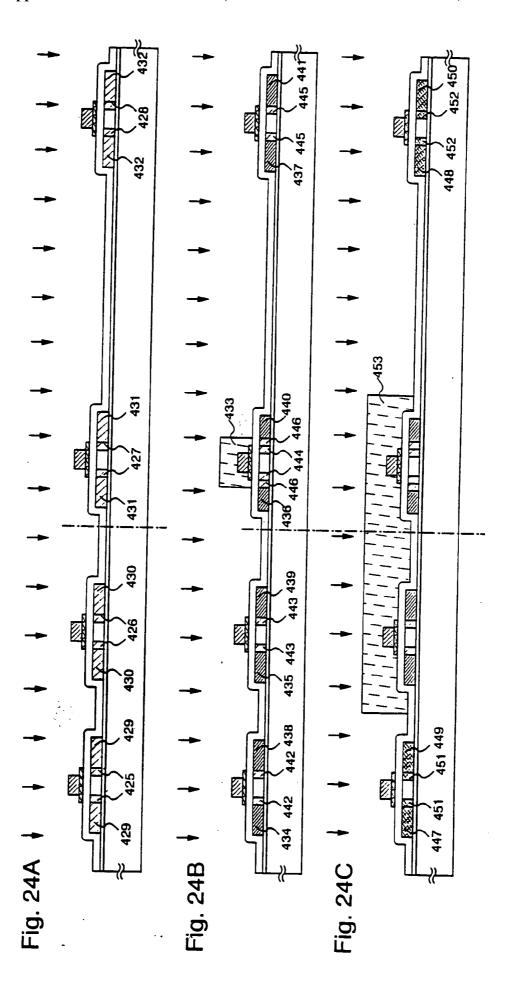

[0071] FIGS. 24A through 24C are cross-sectional views for illustrating various steps of a fabricating method of a light emitting device.

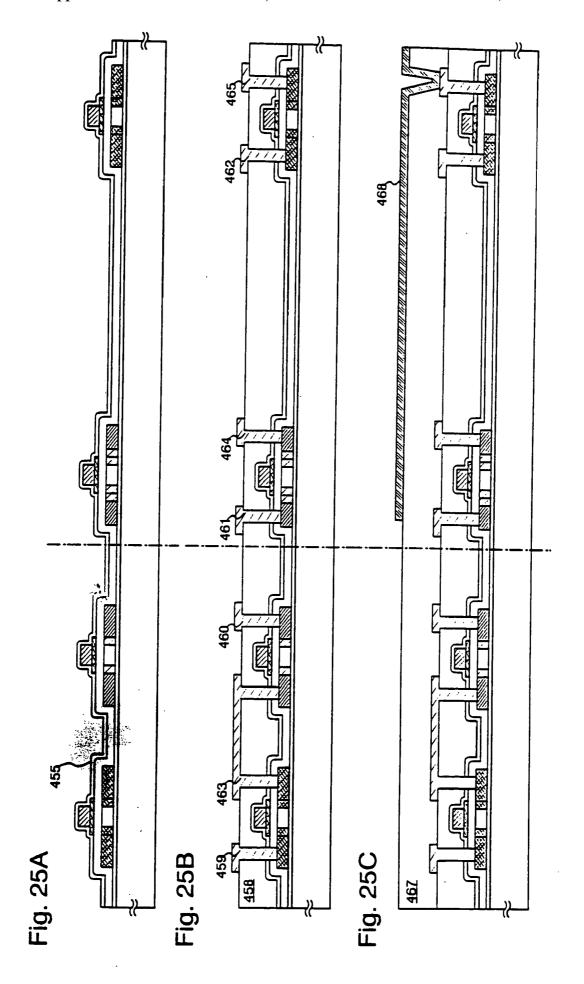

[0072] FIGS. 25A through 25C are cross-sectional views for illustrating various steps of a fabricating method of a light emitting device.

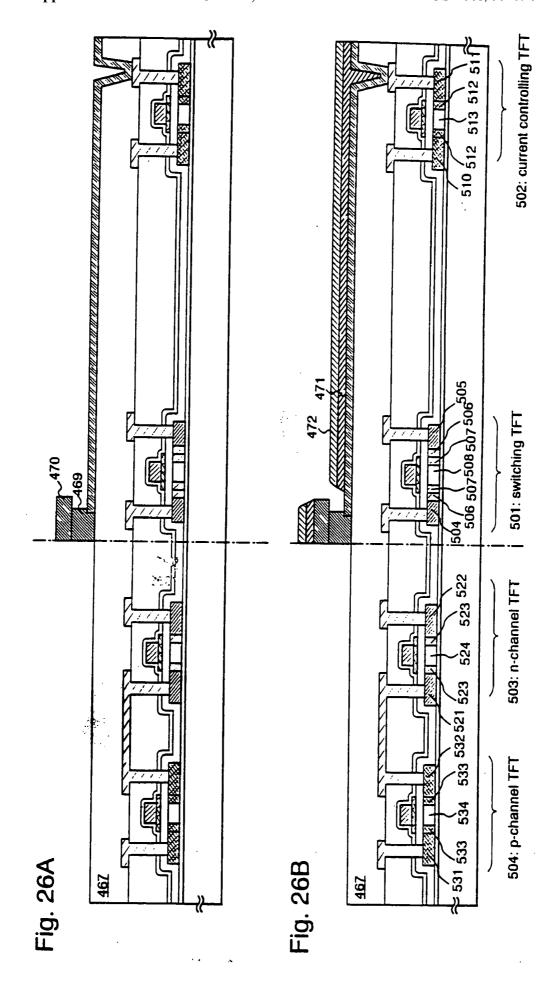

[0073] FIGS. 26A and 26B are cross-sectional views for illustrating various steps of a fabricating method of a light emitting device.

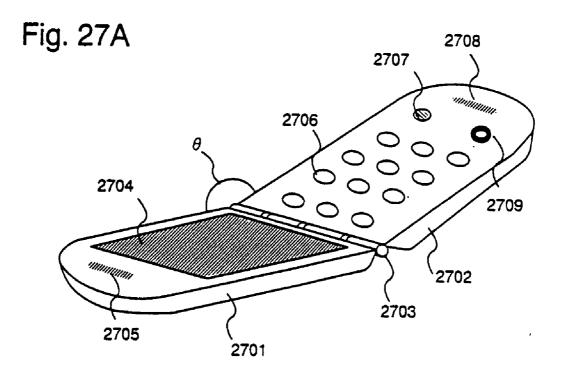

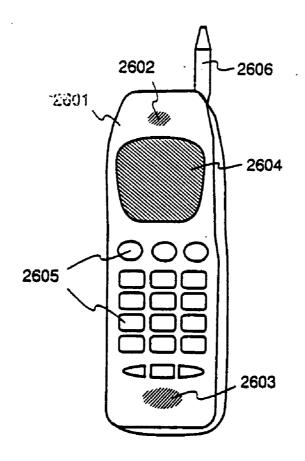

[0074] FIG. 27A and 27B are diagram for illustrating electronic apparatuses each employing a light emitting device in accordance with the present invention.

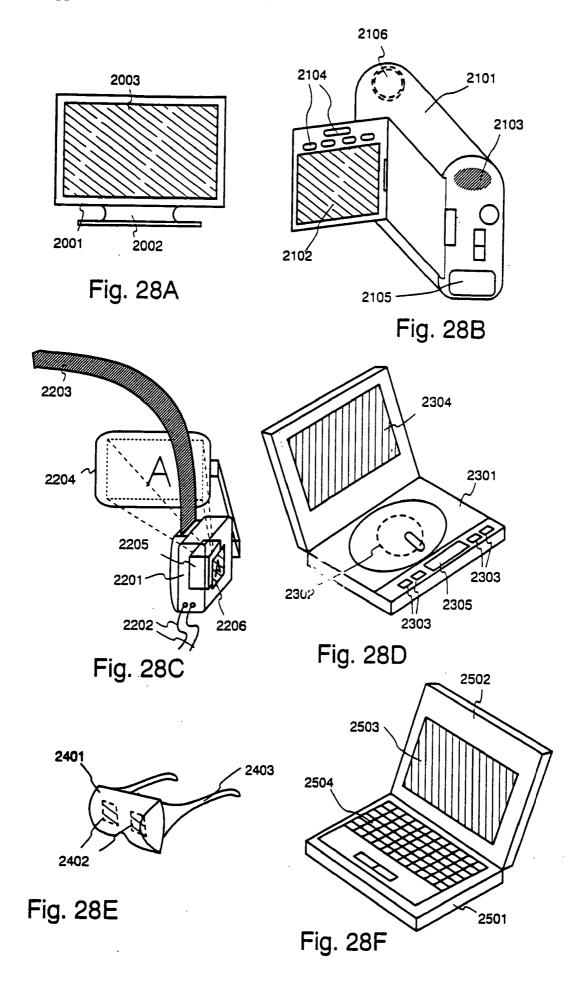

[0075] FIGS. 28A through 28F are diagram for illustrating electronic apparatuses each employing a light emitting device in accordance with the present invention.

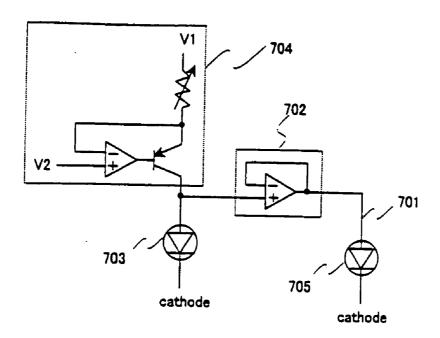

[0076] FIGS. 29A and 29B show a connection of a light emitting element for a monitor of the light emitting device of the present invention, and a characteristic in measurement values of brightness due to temperatures of the light emitting element, respectively.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

### Embodiment Mode 1

[0077] A first structure in accordance with the present invention will be now described. FIG. 1 shows a block diagram of a light emitting device having the first structure in accordance with the present invention.

[0078] Reference numeral 101 denotes a pixel portion in which a plurality of pixels are provided in matrix. Reference numerals 102 and 103 denote a source signal line driver circuit and a gate signal line driver circuit, respectively.

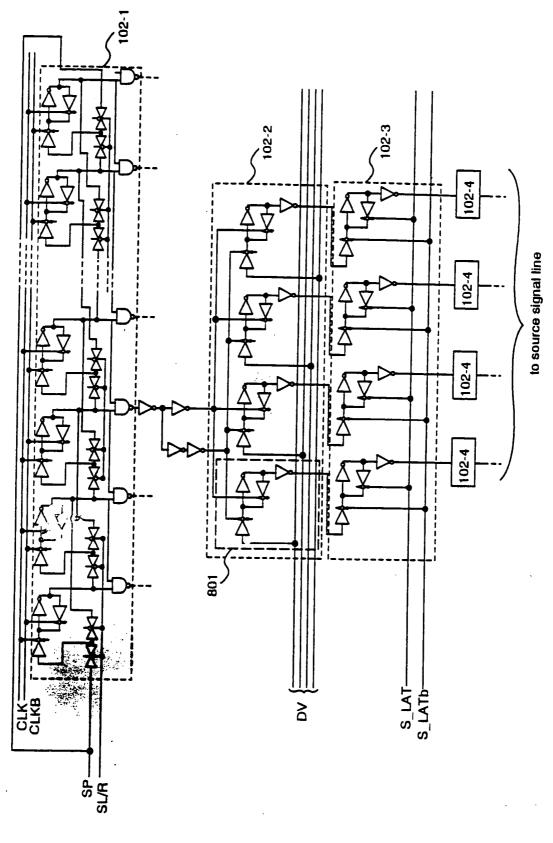

[0079] The source signal line driver circuit 102 includes a shift register 102-1, a latch (A) 102-2, a latch (B) 102-3, and a switching circuit 102-4. It should be noted that the source signal line driver circuit of the present invention may further include a level shift, a buffer or the like, in addition to the components mentioned above.

[0080] Although not illustrated, the gate signal line driver circuit 103 includes a shift register and a buffer. In some cases, the gate signal line driver circuit 103 may further include a level shift in addition to the shift register and the buffer. Gate electrodes of pixel TFTs in one row are connected to one gate signal line, and therefore, all of the pixels TFTs in one row have to be simultaneously turned on. Accordingly, a buffer capable of allowing a large current to flow therethrough is used.

[0081] In the source signal line driver circuit 102, a clock signal (CLK) and a start pulse (SP) are input into the shift register 102-1. The shift register 102-1 sequentially generates a timing signal based on these clock signal (CLK) and start pulse (SP) and supplies the generated timing signal sequentially to a circuit in the succeeding stage.

[0082] The timing signal to be output from the shift register 102-1 may be sequentially supplied to the circuit in the succeeding stage through a buffer or the like (not illustrated). The timing signal from the shift register 102-1 is buffered and amplified by the buffer or the like. Since a number of circuits or elements are connected to a wiring to which the timing signal is to be supplied, a large load capacitance (parasitic capacitance) exists. In order to prevent a rising edge or a trailing edge of the timing signal from being rounded due to such a large load capacitance, the above-mentioned buffer is provided.

[0083] The timing signal output from the shift register 102-1 is supplied to the latch (A) 102-2. The latch (A) 102-2 includes latches in multiple stages for processing an n-bit S digital video signal. When the timing signal is input to the latch (A) 102-2, it sequentially takes in the n-bit digital video signal to be externally supplied to the source signal line driver circuit 102 and held them therein.

[0084] When the digital video signal is taken in into the latch (A) 102-2, the digital video signal may be sequentially input into the latches in the multiple stages included in the latch (A) 102-2. However, the present invention is not limited to such a structure. A so-called division driving may be performed in which the latches in the multiple stages included in the latch (A) 102-2 are divided into several groups and the digital video signal is input every group in parallel and simultaneously. In such a case, the number of the groups is referred to as the division number. For example, in the case where the latches are divided into four groups, it can be said that the device is driven through the quarter-division scheme.

[0085] A time period required for completing all of the writing of the digital video signal into the latches in all of the stages of the latch (A) 102-2 is referred to as a line period. More specifically, the line period refers to a time period measured from a timing when the writing of the digital video signal into the latch in the leftmost stage in the latch (A) 102-2 starts until a timing when the writing of the digital video signal into the latch in the rightmost stage ends. In practice, the line period may include a horizontal blanking period in addition to the above-described line period.

[0086] After the one line period ends, latch signals are supplied to the latch (B) 102-3. At this moment, the digital video signal that has been written into and held at the latch (A) 102-2 is simultaneously sent out to the latch (B) 102-3 to be written into latches in all of the stages of the latch (B) 102-3 and held therein.

[0087] Further digital video signal to be externally supplied to the source signal line driver circuit 102 is again sequentially written, based on the timing signal from the shift register 102-1, into the latch (A) 102-2 from which the previous digital video signal was sent out to the latch (B) 102-3.

[0088] During the second turn of the one line period, the digital video signal that has been written into and held at the latch (B) 102-3 is simultaneously sent out to the switching circuit 102-4. The switching circuit 102-4 causes the polarity of the digital video signal input from the latch (B) 102-2 to be inverted, or alternatively allows the polarity of those digital video signal not to be inverted, in accordance with shift signals, and outputs the resultant signals.

[0089] The digital video signal includes information of either "0" or "1". The digital video signal corresponding to "0" is a signal having a Hi potential, while the digital video signal corresponding to "1" is a signal having a Lo potential, or vice versa. The inversion of the polarity of the digital video signal means that the digital video signal having information of "0" is converted into that having information of "1", while the digital video signal having information of "1" is converted into that having information of "0".

[0090] The shift signal is a signal to be used for selecting whether the polarity of the digital video signal input from the latch (B) 102-2 is to be inverted or not. The polarity of the digital video signal is inverted by the shift signal when an average of a time period during which all of the light emitting elements emit light in one frame period becomes longer than a half of a time period during which the light emitting elements emit light in one frame period in the case where the totally white is to be displayed in the pixel portion **101**, thereby resulting in power consumption being reduced. On the other hand, when an average of the time period during which all of the light emitting elements emit light in one frame period becomes shorter than a half of the time period during which the light emitting elements emit light in one frame period in the case where the totally white is to be displayed in the pixel portion 101, the polarity of the digital video signal is not allowed to be inverted in accordance with the shift signal, for the purpose of suppressing the power consumption.

[0091] Whether the polarity of the digital video signal should be inverted or not in accordance with the shift signal may be chosen by a user, or alternatively, may be automatically chosen based on an image to be displayed.

[0092] The digital video signal output from the switching circuit 102-4 is input into the source signal lines.

[0093] On the other hand, in the gate signal line driver circuit 103, a gate signal from a shift register (not illustrated) is input into a buffer (not illustrated), and further input into a corresponding gate signal line (also referred to as a scanning line).

[0094] In accordance with the gate signal input into the gate signal line, the digital video signal input into the source signal lines is input into the pixels.

[0095] In the above description, the source signal line driver circuit 102 and the gate signal line driver circuit 103 may be provided on the same substrate as the pixel portion 101. Alternatively, those driver circuits 102 and 103 may be provided on an IC chip and connected to the pixel portion 101 via some techniques such as FPC or TAB.

[0096] In accordance with the above-mentioned structure of the present embodiment of the invention, in the case where the light emitting device for performing a digitally-driven time-divisional gradation display displays a monochrome image, the contrast of an image can be inverted based on natures of the image to be displayed in the pixel portion. More specifically, the contrast of the image to be displayed in the pixel portion is inverted when an average of a time period during which all of the light emitting elements emit light in one frame period becomes longer than a half of a time period during which the light emitting elements emit light in one frame period in the case where the totally white is to be displayed in the pixel portion 101. On the other hand,

when an average of the time period during which all of the light emitting elements emit light in one frame period becomes shorter than a half of the time period during which the light emitting elements emit light in one frame period in the case where the totally white is to be displayed in the pixel portion 101, it is desirable that the contrast of the image to be displayed in the pixel portion is not allowed to be inverted.

[0097] In the above description of the present embodiment, the switching circuit is included in the source signal line driver circuit. Alternatively, it is acceptable that the switching circuit is not included in the source signal line driver circuit.

[0098] In the present embodiment mode, only the situation where the digital video signal is employed has been described. Alternatively, the present invention may be applied to the case where an analog video signal is used instead of the digital video signal.

[0099] Accordingly, the magnitude of a current to flow through the light emitting element can be suppressed to some extent in accordance with the first structure of the present invention, thereby resulting in the power consumption of the resultant light emitting device being suppressed.

### Embodiment Mode 2

[0100] A second structure in accordance with the present invention will be now described. FIG. 2 shows a block diagram of a light emitting device having the second structure in accordance with the present invention. In FIG. 2, the same components as shown in FIG. 1 are designated with the same reference numerals.

[0101] The light emitting device in the present embodiment mode employs a clock signal control circuit 106 which allows a constant electrical potential instead of the clock signal (CLK) to be applied to the shift register 102-1.

[0102] More specifically, the light emitting device is configured to input a constant electrical potential (fixed electrical potential) into the shift register 102-1, instead of the clock signal, for a constant time period by means of the clock signal control circuit 106. The above structure prevents the timing signal that is to be used for inputting the digital video signal at less significant bits in the range from the first bit to the m-th bit (m is any integer in the range from 1 to n) into the latch (A) 102-2 from being input into the latch (A) 102-2. Accordingly, only the digital video signal at more significant bits in the range from the (m+1)-th bit to the n-th bit can be written into the latch (A) 102-2.

[0103] The light emitting device in the present embodiment mode is different from that shown in FIG. 1 in that the source signal line driver circuit 102 does not include the switching circuit 102-4. Accordingly, the digital video signal that has been written into and held at the latch (B) 102-3 is input into the source signal lines by means of the latch signal to be input into the latch (B) 102-3.

[0104] In accordance with the present embodiment mode, in the light emitting device that performs a digitally-driven time-divisional gradation display, the digital video signal input into the source signal line driver circuit contained in the light emitting device is input into the pixel portion after the number of bits thereof is reduced. More specifically, the

number of bits of the digital video signal to be input into the pixel portion is reduced by sequentially cutting off a bit of the digital video signal from the least significant bit.

[0105] In accordance with the above-described structure, the number of bits of the digital video signal to be input into the pixel portion is reduced, and therefore, the required number of writing the digital video signal into the pixels by means of the source signal line driver circuit and the gate signal line driver circuit can be reduced. Thus, the power consumption of the source signal line driver circuit and the gate signal line driver circuit can be suppressed, thereby resulting in the power consumption of the light emitting device being suppressed.

[0106] It should be noted that in the present embodiment mode, the clock signal control circuit 106 may be provided on the same substrate as the pixel portion 101, or alternatively, may be formed in an IC chip.

## Embodiment Mode 3

[0107] Another example of the second structure in accordance with the present invention, which is different from the one described in Embodiment Mode 2, will be now described. FIG. 3 shows a block diagram of a light emitting device having the second structure in accordance with the present invention. In FIG. 3, the same components as shown in FIG. 1 are designated with the same reference numerals.

[0108] The light emitting device in the present embodiment mode employs a timing signal control circuit 107 which allows a constant electrical potential, instead of the timing signal output from the shift register 102-1, to be applied to the latch (A) 102-2.

[0109] More specifically, the light emitting device is configured to input a constant electrical potential (fixed electrical potential) into the latch (A) 102-2, instead of the timing signal output from the shift register 102-1, for a constant time period by means of the timing signal control circuit 107. The above structure prevents the timing signal that is to be used for inputting the digital video signal at less significant bits in the range from the first bit to the m-th bit (m is any integer in the range from 1 to n) into the latch (A) 102-2 from being input into the latch (A) 102-2. Accordingly, only the digital video signal at more significant bits in the range from the (m+1)-th bit to the n-th bit can be written into the latch (A) 102-2.

[0110] It should be noted that in the present embodiment mode, the fixed electrical potential is required to be at such a level that prevents the digital video signal from being written into the latch (A) 102-2.

[0111] In accordance with the present embodiment mode, in the light emitting device that performs a digitally-driven time-divisional gradation display, the digital video signal input into the source signal line driver circuit contained in the light emitting device is input into the pixel portion after the number of bits thereof is reduced. More specifically, the number of bits of the digital video signal to be input into the pixel portion is reduced by sequentially cutting off the bit of the digital video signal from the least significant bit.

[0112] In accordance with the above-described structure, the number of bits of the digital video signal to be input into the pixel portion is reduced, and therefore, the required

number of writing the digital video signal into the pixels by means of the source signal line driver circuit and the gate signal line driver circuit can be reduced. Thus, the power consumption of the source signal line driver circuit and the gate signal line driver circuit can be suppressed, thereby resulting in the power consumption of the light emitting device being suppressed.

[0113] It should be noted that in the present embodiment mode, the timing signal control circuit 107 may be provided on the same substrate as the pixel portion 101, or alternatively, may be formed in an IC chip.

#### Embodiment Mode 4

[0114] Still another example of the second structure in accordance with the present invention, which is different from the ones described in Embodiment Modes 2 and 3, will be now described. FIG. 4 shows a block diagram of a light emitting device having the second structure in accordance with the present invention. In FIG. 4, the same components as shown in FIG. 1 are designated with the same reference numerals.

[0115] The light emitting device in the present embodiment mode employs a start pulse signal control circuit 108 which allows a constant electrical potential, instead of the start pulse signal (SP), to be applied to the shift register 102-1.

[0116] More specifically, the light emitting device is configured to input a constant electrical potential (fixed electrical potential) into the shift register 102-1, instead of the start pulse signal, for a constant time period by means of the start pulse signal control circuit 108, so that the timing signal that is to be used for inputting the digital video signal at less significant bits in the range from the first bit to the m-th bit (m is any integer in the range from 1 to n) into the latch (A) 102-2. Accordingly, only the digital video signal at more significant bits in the range from the (m+1)-th bit to the n-th bit can be written into the latch (A) 102-2.

[0117] It should be noted that in the present embodiment mode, the fixed electrical potential is required to be at such a level that prevents the timing signal from being output from the shift register 102-1.

[0118] In accordance with the present embodiment mode, in the light emitting device that performs a digitally-driven time-divisional gradation display, the digital video signal input into the source signal line driver circuit contained in the light emitting device is input into the pixel portion after the number of bits thereof is reduced. More specifically, the number of bits of the digital video signal to be input into the pixel portion is reduced by sequentially cutting off the bit of the digital video signal from the least significant bit.

[0119] In accordance with the above-described structure, the number of bits of the digital video signal to be input into the pixel portion is reduced, and therefore, the required number of writing the digital video signal into the pixels by means of the source signal line driver circuit and the gate signal line driver circuit can be reduced. Thus, the power consumption of the source signal line driver circuit and the gate signal line driver circuit can be suppressed, thereby resulting in the power consumption of the light emitting device being suppressed.

[0120] It should be noted that in the present embodiment mode, the start pulse signal control circuit 108 may be provided on the same substrate as the pixel portion 101, or alternatively, may be formed in an IC chip.

#### Embodiment Mode 5

[0121] A third structure in accordance with the present invention will be now described with reference to FIG. 5.

[0122] In FIG. 5, reference numeral 501 denotes a power source line. In the present specification, the power source line refers to a wiring to be used for applying a predetermined electrical potential to a pixel electrode contained in a light emitting element in a pixel section by means of the digital video signal to be input into a source signal line. In the present specification, the electrical potential of the power source line is referred to as the power source potential.

[0123] Reference numeral 502 denotes a buffer amplifier, reference numeral 503 denotes a monitoring light emitting element, and reference numeral 504 denotes a constant current source. One of electrodes of the monitoring light emitting element 503 is connected to the constant current source 504, so that a constant current always flows through the monitoring light emitting element 503. When a temperature of an organic compound layer contained in the light emitting element changes, the magnitude of the current to flow through the monitoring light emitting element 503 does not change, but rather, an electrical potential of the electrode of the monitoring light emitting element 503 connected to the constant current source 504 changes.

[0124] On the other hand, the buffer amplifier 502 includes two input terminals and one output terminal. One of the two input terminals is a non-inverted input terminal (+), while the other is an inverted input terminal (-). An electrical potential at one of electrodes of the monitoring light emitting element 503 is supplied to the buffer amplifier 502.

[0125] The buffer amplifier 502 is a circuit for preventing an electrical potential at a pixel electrode of the monitoring light emitting element 503 connected to the constant current source 504 changes in accordance with a load such as a wiring capacitance of the power source line 501 or the like. Accordingly, the electrical potential provided to the non-inverted input terminal of the buffer amplifier 502 is output from an output terminal to be supplied to the power source line as the power source potential, without being changed in accordance with a load such as a wiring capacitance of the power source line 501 or the like.

[0126] Accordingly, even when a temperature of the monitoring light emitting element 503 or the organic compound layer of the light emitting element in the pixel portion changes due to a change in an environmental temperature, the power source potential is changed so as to allow a constant current to flow through the light emitting element. Thus, even when the environmental temperature of the light emitting device increases, power consumption of the light emitting device can be prevented from increasing.

[0127] In the present embodiment mode, the buffer amplifier 502, the monitoring light emitting element 503, and the constant current source 504 may be provided on the same substrate as the pixel portion, or alternatively, may be formed in an IC chip. Moreover, the monitoring light

emitting element 503 may be included in the pixel portion, or alternatively, may be provided independently of the pixel portion.

[0128] The present invention can suppress power consumption of a light emitting device and an electronic apparatus employing the light emitting device in accordance with the above-described first through third structures. It should be noted that only either one of the first through third structures is required to be included in the present invention, although two or all of the first through third structures may be included.

[0129] The present invention can allow power consumption of the light emitting device to be suppressed by means of the above-described three structures.

#### Embodiments

[0130] Several embodiments will be described below.

## Embodiment 1

[0131] In the present embodiment, the structure of a pixel portion of a light emitting device and its driving method in accordance with the present invention will be described.

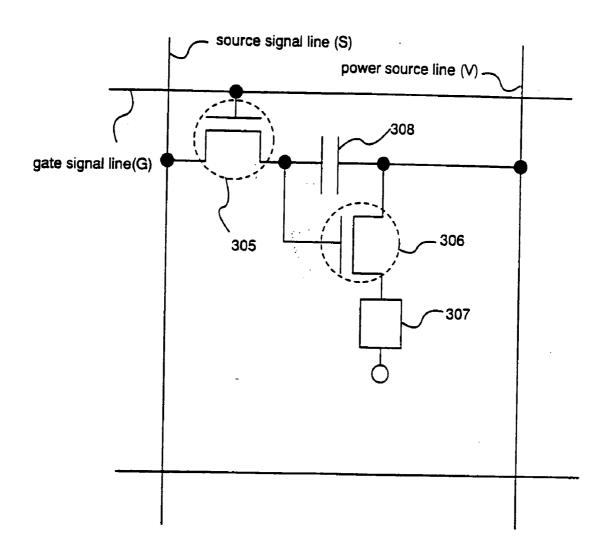

[0132] FIG. 6 shows an expanded view of the pixel portion 301 of the light emitting device in accordance with the present embodiment of the invention. Source signal lines (S1 to Sx), power source lines (V1 to Vx), and gate signal lines (G1 to Gy) are provided in the pixel portion 301.

[0133] In the present embodiment, a pixel 304 refers to a region in which one of the source signal lines (S1 to Sx), one of the power source lines (V1 to Vx), and one of the gate signal lines (G1 to Gy) are provided. In the pixel portion 301, a plurality of the pixels 304 are arranged in matrix.

[0134] An expanded view of the pixel 304 is shown in FIG. 7. In FIG. 7, reference numeral 305 denotes a switching TFT. A gate electrode of the switching TFT 305 is connected to the gate signal line G (G1 to Gx). One of a source region and a drain region of the switching TFT 305 is connected to the source signal line S (S1 to Sx), while the other thereof is connected to a gate electrode 306 of a current-controlling TFT 306 as well as to a capacitor 308 of each pixels.

[0135] The capacitor 308 is provided for holding a gate potential of the current-controlling TFT 306 (an electrical potential difference between the gate electrode and the source region) when the switching TFT 305 is in the non-selected condition (off condition). Although the capacitor 308 is provided in the present embodiment, the present invention is not limited to such a structure. The capacitor 308 may be omitted.

[0136] One of the source region and the drain region of the current-controlling TFT 306 is connected to the power source line V (V1 to Vx), while the other is connected to the light emitting element 307. The power source line V is connected to the capacitor 308.

[0137] The light emitting element 307 is composed of an anode, a cathode, and an organic compound layer provided between the anode and the cathode. In the case where the anode is connected to the source region or the drain region of the current-controlling TFT 306, the anode functions as

the pixel electrode and the cathode functions as a counter electrode. On the other hand, in the case where the cathode is connected to the source region or the drain region of the current-controlling TFT 306, the cathode functions as the pixel electrode and the anode functions as the counter electrode.

[0138] A counter potential is supplied to the counter electrode of the light emitting element 307. In addition, the power source potential is supplied to the power source line V. The power source potential and the counter potential are supplied to the light emitting device of the present invention by means of a power source provided by an externally-attached IC chip or the like.

[0139] The switching TFT 305 and the current-controlling TFT 306 may be either of the n-channel type TFT or the p-channel type TFT. It should be noted, however, that in the case where the source region or the drain region of the current-controlling TFT 306 is connected to the anode of the light emitting element 307, it is preferable that the current-controlling TFT 306 is the p-channel type TFT. On the other hand, in the case where the source region or the drain region of the current-controlling TFT 306 is connected to the cathode of the light emitting element 307, it is preferable that the current-controlling TFT 306 is the n-channel type TFT.

[0140] The switching TFT 305 and the current-controlling TFT 306 may have a multi-gate structure such as a double gate structure, a triple gate structure or the like, rather than a single gate structure.

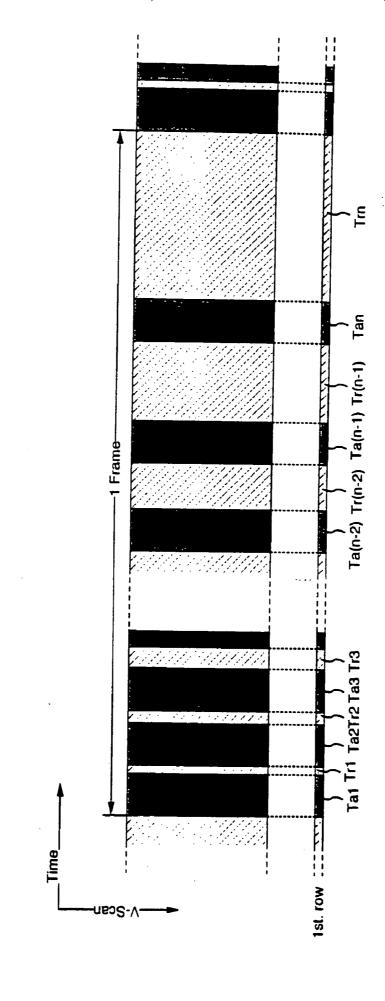

[0141] Then, a driving method of the light emitting device of the present invention that includes the above-mentioned structure will be described with reference to FIG. 8.

[0142] First, the power source potential of the power source line becomes to be equal to an electrical potential of the counter electrode of the light emitting element. Then, a gate signal is input from the gate signal line driver circuit to the gate signal line G1. As a result, the switching TFTs 305 of all of the pixels connected to the gate signal line G1 (i.e., the pixels in the first row) are placed in the ON state.

[0143] Simultaneously, the digital video signal at the first bit is input from the source signal line driver circuit into the source signal lines (S1 to Sx). The digital video signal is input to the gate electrode of the current-controlling TFT 306 via the switching TFT 305.

[0144] Then, at the same time when the input of the gate signal into the G1 is completed, the similar gate signal is input into the next gate signal line G2. Thus, the switching TFTs 305 of all of the pixels connected to the gate signal line G2 (i.e., the pixels in the second row) are placed in the ON state, thereby the digital video signal at the first bit is input from the source signal lines (S1 to Sx) into the pixels in the second row.

[0145] Thereafter, the gate signal is sequentially input to all of the gate signal lines (G1 to Gx). A time period required for selecting all of the gate signal lines (G1 to Gx) and inputting the digital video signal at the first bit into the pixels in all of the rows is a writing period Ta1.

[0146] When the writing period Ta1 is completed, a light emitting period Tr1 then starts. During the light emitting period Tr1, the power source potential of the power source

line comes to be at such a potential level that provides a potential difference with respect to the counter electrode, so that the light emitting element can emit light when the power source potential is supplied to the pixel electrode of the light emitting element.

[0147] In the present embodiment, in the case where the digital video signal has information of "0", the current-controlling TFT 306 is in the OFF state. Accordingly, the power source potential is not supplied to the pixel electrode of the light emitting element 307. As a result, the light emitting element 307 included in the pixel to which the digital video signal having information of "0" is supplied does not emit light.

[0148] On the other hand, in the case where the digital video signal has information of "1", the current-controlling TFT 306 is in the ON state. Accordingly, the power source potential is supplied to the pixel electrode of the light emitting element 307. As a result, the light emitting element 307 included in the pixel to which the digital video signal having information of "1" is supplied emits light.

[0149] Thus, during the display period Tr1, the light emitting element 307 is placed either in the emission state or the non-emission state, so that all of the pixels perform a display operation. A time period during which the pixel performs the display operation is referred to as a display period Tr. More specifically, the display period that starts when the digital video signal at the first bit is input into the pixel is referred to as Tr1. In FIG. 8, only the display period of the pixels in the first row is illustrated for the purpose of simplification of the description. Timings at which the respective display periods for all of the rows start are the same.

[0150] When the display period Tr1 is completed, a next writing period Ta2 starts, and the power source potential of the power source line comes to be equal to the electrical potential of the counter electrode of the light emitting element. Similarly in the case of the writing period Ta1, all of the gate signal lines are sequentially selected, and the digital video signal at the second bit is input into all of the pixels. A time period required for completing the input of the digital video signal at the second bit into the pixels in all of the rows is referred to as a writing period Ta2.

[0151] When the writing period Ta2 is completed, a display period Tr2 then starts, and the power source potential of the power source line comes to be at such a potential level that provides a potential difference with respect to the counter electrode, so that the light emitting element can emit light when the power source potential is supplied to the pixel electrode of the light emitting element. Thus, all of the pixels perform the display operation.

[0152] The above-described operations are repeated until the digital video signal at the n-th bit is input into the pixels, so that the writing period Ta and the display period Tr appear alternately. After all of the display periods (Tr1 to Trn) are completed, one image can be displayed. In the driving method in accordance with the present invention, a time period required for displaying one image is referred to as one frame period (F). After a certain one frame period (F) is completed, the next one frame period is started. The writing period Ta1 again appears, and the above-described operations are repeated.

[0153] In a normal light emitting device, it is preferable to provide 60 or more frame periods per one second. If the number of images to be displayed in one second is smaller than 60, flickering of the image may become visually significant.

**[0154]** In the present embodiment, it is necessary that the sum of all of the writing periods is shorter than one frame period and ratios among the respective display periods are set to satisfy the relationship of  $Tr1:Tr2:Tr3:\ldots:Tr(n-1)$ :  $Trn=2^0: 2^1: 2^2:\ldots: 2^{(n-2)}: 2^{(n-1)}$ . Through the combination of the display periods, a desired gradation display among the total of  $2^n$  gradations can be realized.

[0155] The gradation to be displayed by a particular pixel in a certain one frame period is determined by obtaining the sum of the display periods during which the light emitting element emits light in that frame period. For example, assuming that n=8 and the brightness obtained when the pixel emits light in all of the display periods is expressed as 100%, the brightness of 1% can be realized in the case where the pixel emits light in Tr1 and Tr2, while the brightness of 60% can be realized when Tr3, Tr5, and Tr8 are selected.

[0156] The display periods Tr1 through Trn may appear on any order. For example, during one frame period, the display periods may be controlled to appear in such an order that Tr1 is followed by Tr3, Tr5, Tr2, . . . .

[0157] Although the level of the power source potential at the power source line is changed by means of the writing period and the display period in the above description of the present embodiment, the present invention is not limited thereto. A potential difference which allows the light emitting element to emit light when the power source potential is supplied to the pixel electrode of the light emitting element may be controlled to always exist between the power source potential and the electrical potential at the counter electrode. In such a case, the light emitting element can emit light even in the writing period. Accordingly, the gradation to be displayed by a particular pixel in a certain frame period is determined by the sum of the writing periods and the display periods during which the light emitting element emits light in that frame period. In this case, it is necessary that the sum of the writing periods and the display periods corresponding to the digital video signal at the respective bits is set to satisfy the relationship of (Ta1+Tr1):  $(Ta2+Tr2):(Ta3+Tr3): \dots : (Ta(n-1)+Tr(n-1)):(Tan+Trn)=2^0: 2^1: 2^2: \dots : 2^{(n-2)}: 2^{(n-1)}.$

### Embodiment 2

[0158] In the present embodiment, another example of the structure of a pixel portion of a light emitting device and its driving method in accordance with the present invention, different from those in the Embodiment 1, will be described.

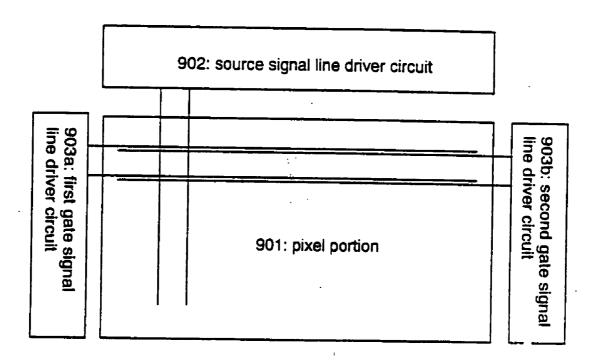

[0159] FIG. 9 shows an exemplary block diagram of a light emitting device in the present embodiment. The light emitting device in FIG. 9 includes a pixel portion 901 by TFT formed on the substrate and includes a source signal side driver circuit 902, a writing gate signal side driver circuit (first gate signal line driver circuit) 903a, and an erasure gate signal line driver circuit (second gate signal line driver circuit) 903b, each provided in the periphery of the pixel portion. Although the light emitting device with one source signal side driver circuit is described in the present embodiment, two of the source signal side driver circuits may be provided.

[0160] The source signal side driver circuit 902 has at least one of the first through third structures of the present invention described previously.

[0161] In the present embodiment, the source signal line driver circuit 902 and the writing gate signal side driver circuit 903a and the erasure gate signal line driver circuit 903b may be provided on the same substrate as the pixel portion 901, or alternatively, may be formed on an IC chip and connected to the pixel portion 901 via a certain connector such as FPC, TAB or the like.

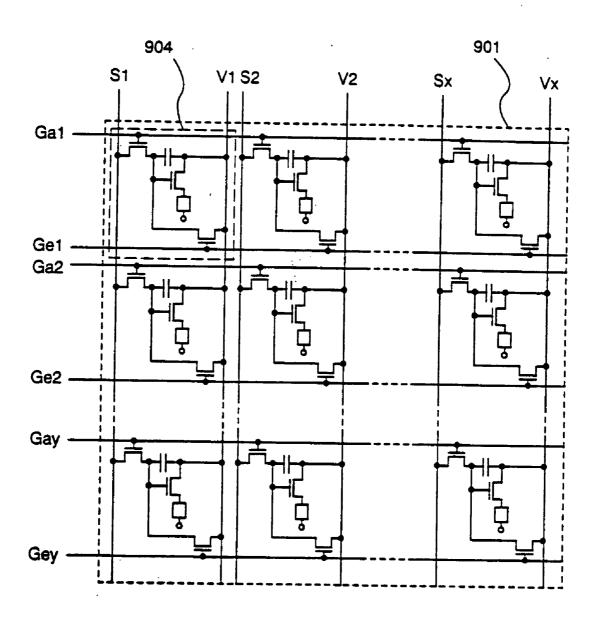

[0162] An expanded view of the pixel portion 901 is shown in FIG. 10. In FIG. 10, source signal lines (S1 to Sx), power source lines (V1 to Vx), and writing gate signal lines (first gate signal lines) (Ga1 to Gay), and erasure gate signal lines (second gate signal lines) (Ge1 to Gey) are provided in the pixel portion 901.

[0163] The pixel 904 refers to a region in which one of the source signal lines (S1 to Sx), one of the power source lines (V1 to Vx), one of the writing gate signal lines (Ga1 to Gay), and one of the erasure gate signal lines (Ge1 to Gey) are provided. In the pixel portion 901, a plurality of the pixels 904 are arranged in matrix.

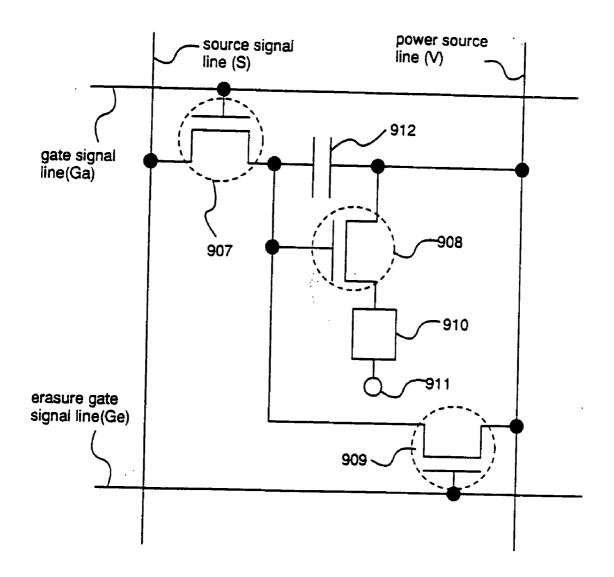

[0164] An expanded view of the pixel 904 is shown in FIG. 11. In FIG. 11, reference numeral 907 denotes the switching TFT. A gate electrode of the switching TFT 907 is connected to the gate signal line Ga (Ga1 to Gay). One of a source region and a drain region of the switching TFT 907 is connected to the source signal line S (S1 to Sx), while the other thereof is connected to a gate electrode of a current-controlling TFT 908 as well as to a capacitor 912 and source and drain regions of an erasure TFT 909 included in each pixels.

[0165] The capacitor 912 is provided for holding a gate potential of the current-controlling TFT 908 when the switching TFT 907 is in the non-selected condition (off condition). Although the capacitor 912 is provided in the present embodiment, the present invention is not limited to such a structure. The capacitor 912 may be omitted.

[0166] One of the source region and the drain region of the current-controlling TFT 908 is connected to the power source line V (V1 to Vx), while the other thereof is connected to the light emitting element 910. The power source line V is connected to the capacitor 912.

[0167] One of the source region and the drain region of the erasure TFT 909 that is not connected to the source or drain region of the switching TFT 907 is connected to the power source line V. A gate electrode of the erasure TFT 909 is connected to the erasure gate signal line Ge.

[0168] The light emitting element 910 is composed of an anode, a cathode, and an organic compound layer provided between the anode and the cathode. In the case where the anode is connected to the source region or the drain region of the current-controlling TFT 908, the anode functions as the pixel electrode and the cathode functions as a counter electrode. On the other hand, in the case where the cathode is connected to the source region or the drain region of the current-controlling TFT 908, the cathode functions as the pixel electrode and the anode functions as the counter electrode.

[0169] A counter potential is supplied to the counter electrode 911 of the light emitting element 910. In addition, the power source potential is supplied to the power source line V. A potential difference between the counter potential and the power source potential is always maintained at such a level that causes the light emitting element to emit light when the power source potential is applied to the pixel electrode. The power source potential and the counter potential are supplied to the light emitting device of the present invention by means of a power source provided by an externally-attached IC chip or the like.

[0170] In the typical light emitting device to date, when the amount of light emission per unit light emission area of a pixel is 200 cd/m², a current of several mA/cm² per unit area of a pixel portion is required to flow. Thus, especially with a larger display area, it becomes difficult to control the magnitude of the electrical potential to be supplied from the power source provided in the IC chip by means of a switch. In the present embodiment, the power source potential and the counter potential are always maintained to be constant, and therefore, the magnitude of the electrical potential to be supplied from the power source provided in the IC chip is not required to be controlled by means of a switch. Accordingly, the present embodiment is useful for realizing a panel having a larger display size.

[0171] The switching TFT 907, the current-controlling TFT 908, and the erasure TFT 909 may be either of the n-channel type TFT or the p-channel type TFT. It should be noted, however, that in the case where the source region or the drain region of the current-controlling TFT 908 is connected to the anode of the light emitting element 910, it is preferable that the current-controlling TFT 908 is the p-channel type TFT. On the other hand, in the case where the source region or the drain region of the current-controlling TFT 908 is connected to the cathode of the light emitting element 910, it is preferable that the current-controlling TFT 908 is the n-channel type TFT.

[0172] The switching TFT 907, the current-controlling TFT 908, and the erasure TFT 909 may have a multi-gate structure such as a double gate structure, a triple gate structure or the like, rather than a single gate structure.

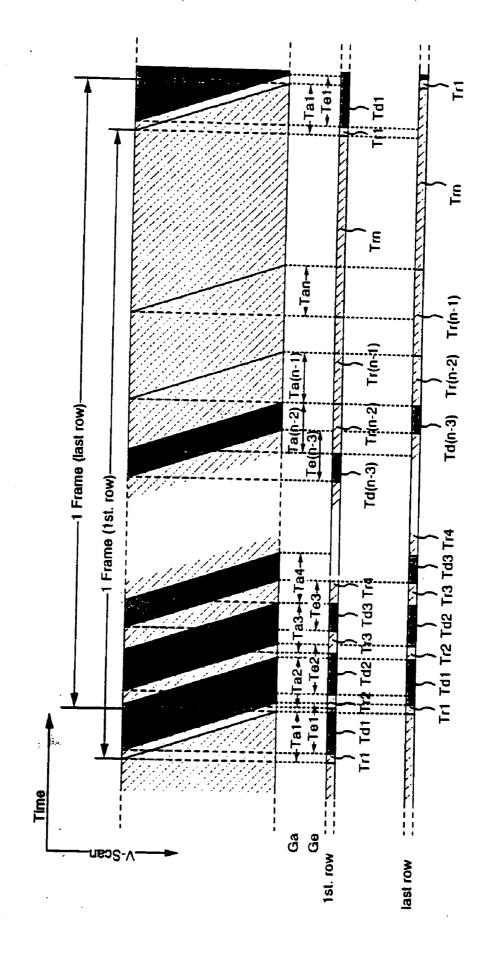

[0173] Then, a driving method of the light emitting device of the present invention that includes the above-mentioned structure will be described with reference to FIG. 12.

[0174] First, a writing gate signal is input from the writing gate signal line driver circuit 903a to the writing gate signal line Ga1, and thus, the switching TFTs 907 of all of the pixels connected to the writing gate signal line Ga1 (i.e., the pixels in the first row) are placed in the ON state. In the present specification, when all of the TFTs having a gate electrode connected to a certain signal line, the signal line is referred to as being selected. Thus, in the above-described case, the writing gate signal line Ga1 is being selected.

[0175] Simultaneously, the digital video signal at the first bit is input from the source signal line driver circuit 902 into the source signal lines (S1 to Sx). More specifically, the digital video signal is input to the gate electrode of the current-controlling TFT 908 via the switching TFT 907.

[0176] In the present embodiment, in the case where the digital video signal has information of "0", the current-controlling TFT 908 is in the OFF state. Accordingly, the

power source potential is not supplied to the pixel electrode of the light emitting element 910. As a result, the light emitting element 910 included in the pixel to which the digital video signal having information of "0" is supplied does not emit light.

[0177] On the other hand, in the case where the digital video signal has information of "1", the current-controlling TFT 908 is in the ON state. Accordingly, the power source potential is supplied to the pixel electrode of the light emitting element 910. As a result, the light emitting element 910 included in the pixel to which the digital video signal having information of "1" is supplied emits light.

[0178] Thus, at the same time when the digital video signal is input into the pixels in the first row, the light emitting element is placed either in the emission state or the non-emission state, so that all of the pixels in the first row perform a display operation. A time period during which the pixel performs the display operation is referred to as a display period Tr. More specifically, the display period that starts when the digital video signal at the first bit is input into the pixel is referred to as Tr1. In FIG. 12, only the display period of the pixels in the first row is illustrated for the purpose of simplification of the description. Timings at which the display periods for the respective rows start are offset from each other by a certain time difference.

[0179] Then, at the same time when the selection of the Ga1 is completed, the next writing gate signal line Ga2 is selected by the writing gate signal. Thus, the switching TFTs 907 of all of the pixels connected to the writing gate signal line Ga2 are placed in the ON state, thereby the digital video signal at the first bit is input from the source signal lines (S1 to Sx) into the pixels in the second row.

[0180] Thereafter, all of the writing gate signal lines (Ga1 to Gax) are sequentially selected. A time period required for selecting all of the writing gate signal lines (Ga1 to Gax) and inputting the digital video signal at the first bit into the pixels in all of the rows is a writing period Ta1.

[0181] On the other hand, before the digital video signal at the first bit is input into the pixels in all of the rows, in other words, before the writing period Ta1 is completed, the erasure gate signal line Ge1 is selected by an erasure gate signal to be input from the erasure gate signal line driver circuit 903b, in parallel to the input of the digital video signal of the first bit into the pixels.

[0182] When the erasure gate signal line Ge1 is selected, the erasure TFTs 909 in all of the pixels connected to the erasure gate signal line Ge1 (the pixels in the first row) are placed in the ON state. Thus, the power source potential of the power source line (V1 to Vx) is supplied to the gate electrodes of the current-controlling TFTs 908 in the pixels in the first row.

[0183] When the power source potential is supplied to the gate electrodes of the current-controlling TFTs 908, the current-controlling TFTs 908 are placed in the OFF state. Thus, the power source potential is not supplied to the pixel electrodes of the light emitting elements 910, so that all of the light emitting elements included in the pixels in the first row are placed in the non-emission state. Thus, the pixels in the first row do not performs a display operation. In other words, the digital video signal that has been held at the gate electrode of the current-controlling TFT since the selection

of the writing gate signal line Ga1 is erased when the power source potential is supplied to the gate electrode of the current-controlling TFT. Thus, the pixels in the first row do not performs a display operation.

[0184] A time period during which the pixel does not perform a display operation is referred to as a non-display period Td. The display period Tr1 for the pixels in the first row is completed simultaneously when the erasure gate signal is input into the erasure gate signal line Ge1, and the non-display period Td1 starts.

[0185] In FIG. 12, only the non-display period for the pixels in the first row is particularly illustrated for the purpose of simplification of the description. Timings at which the non-display periods for the respective rows start are offset from each other by a certain time difference.

[0186] Then, at the same time when the selection of the Ge1 is completed, the next erasure gate signal line Ge2 is selected by the erasure gate signal. Thus, the erasure TFTs 909 of all of the pixels connected to the erasure gate signal line Ge2 (the pixels in the second row) are placed in the ON state. The power source potential of the power source lines (V1 to Vx) is supplied to the gate electrode of the currentcontrolling TFT 908 via the erasure TFT 909. When the power source potential is supplied to the gate electrode of the current-controlling TFT 908, the current-controlling TFT 908 is placed in the OFF state. Thus, the power source potential is not supplied to the pixel electrode of the light emitting element 910, so that all of the light emitting elements included in the pixels in the second row are placed in the non-emission state. Thus, the pixels in the second row do not performs a display operation and are placed in the non-display state.

[0187] Then, all of the erasure gate signal lines are sequentially selected by the erasure gate signal. A time period required for selecting all of the erasure gate signal lines (Ga1 to Gax) and erasing the digital video signal at the first bit held in the pixels in all of the rows is referred to as the erasure period Te1.

[0188] On the other hand, before the digital video signal at the first bit held in the pixels in all of the rows is erased, in other words, before the erasure period Te1 is completed, the writing gate signal line Ga1 is again selected, in parallel to the erasure of the digital video signal at the first bit in the pixels. Thus, the pixels in the first row again perform the display operation. The non-display period Td1 is thus completed, and a display period Tr2 starts.

[0189] Thereafter, all of the writing gate signal lines are sequentially selected in the similar manner as described before, and the digital video signal at the second bit is input into all of the pixels. A time period required for inputting the digital video signal at the second bit into the pixels in all of the rows is referred to as a writing period Ta2.